HTML

-

激光成像雷达系统是一种用于探测目标3维信息的主动感知系统,具有高速、高精度、高分辨率、抗电磁干扰等特点,自20世纪90年代以来得到了广泛的应用和发展,目前各国对其的研究仍在不断深化和拓展[1]。激光成像雷达在制导、高分辨率对地观测、高精度激光3维测绘等高速3维成像领域有广泛用途,国外如美国ASC公司、Voxtel公司等已有成熟产品;国内处于起步阶段,西南技术物理研究所、中国电子科技集团第四十四研究所和上海技术物理研究所等企业正在开展相关研究。

雪崩光电二极管(avalanche photodiode,APD) 有盖革和线性两种工作模式[2]。当偏置电压高于其雪崩电压时,APD增益迅速增加,此时单个光子吸收即可使探测器输出电流达到饱和,这种工作状态称为盖革模式。当APD的偏置电压低于其击穿电压时, 对入射光电子起到线性放大作用, 这种工作状态称为线性模式。在线性模式下,反向电压越高,增益就越大。APD对输入的光电子进行等增益放大后形成连续电流,获得带有时间信息的激光连续回波信号。盖革模式具有单光子探测能力,但存在后脉冲,虚警率较高,需要多帧累积成像。线性模式成像速度快,没有死时间和后脉冲,可单帧获取目标的强度和时间图像,在一定条件下也可以实现单光子探测。线性模式探测器适用于需要对目标进行快速、高精度3维成像的场合。

随着APD焦平面器件的不断进步,整体探测器系统的发展受到一定的制约,这个制约因素与光敏芯片后级读出电路的设计与制造密切相关[3]。像素电路设计中需解决微弱光电流的捕获、时间行走误差等问题。大规模阵列读出电路设计中也面临着高频数字信号对敏感模拟电路的干扰、读出电路阵列集成度、帧读出速度等挑战[3]。通过创新优化读出电路架构以提升激光探测器系统性能,是目前3维成像用线性模式APD焦平面探测器的研究方向之一。

本文中针对线性激光焦平面探测器3维成像的应用需求,对两种读出电路架构进行了深入的分析和比较,介绍了读出电路像素单元的关键模块电路,以及前置放大器的类型、探测强度信息和时间信息等模块的研究进展。

-

读出电路目前主要有两种读出架构:一是顺序存取型;二是事件驱动型。顺序存取型根据读出方式可以从像素逐步读取扩展到按行读取。事件驱动型是像素检测到回波信号后产生一个数字脉冲,并异步产生一个读出通道占用请求后进行读取。本文中只讨论顺序读取型读出电路,事件驱动型读出电路不在此描述。顺序读取型中,根据不同的需求有多种架构,下面列举目前设计中常用的3种架构。

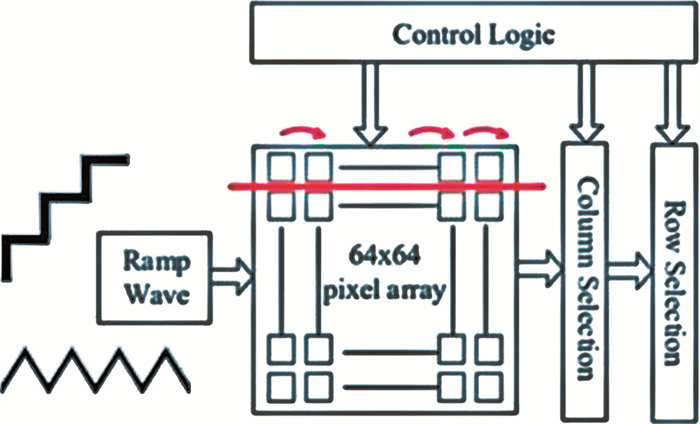

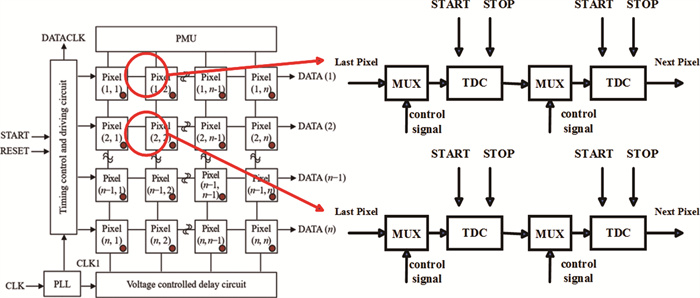

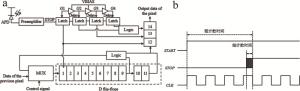

BAI等人设计了一款32×32线性模式焦平面的读出电路,读出电路的架构如图 1所示[4]。像素内采用了时间数字转换器(time-to-digital converter,TDC)计时方式,将时间信息在像素内部转化为数字信号之后,通过时间逻辑控制,利用多路选择器(multiplexer,MUX)将同行的TDC串联,将数字信号串行输出,同时输出32行的数据。每一行的串行输出的数据都包含了这一行的32个像素内TDC的数据,每个TDC包含了14位数据。

Figure 1. 32×32 array circuit diagram[4]

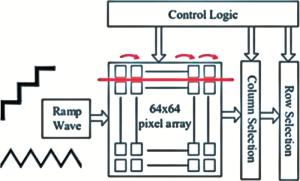

ZHENG设计了一种高精度时间幅度转换器(time-to-amplitude converter,TAC)电路,阵列规模为64×64,其电路将光子飞行时间转化成采样电容上的电压,通过行选电路和列选电路将电压值读出,电路框架如图 2所示[5]。控制逻辑控制第1行选通信号有效时,依次读出此行的第1列、第2列、第3列,直至第1行读完后逻辑控制第2行有效,依次逐步读取每一个像素采样电容上存储的电压值。由于读出电路的每一帧都需将4096个像素内的采样电容上的电压值全部读出,因此成像帧率不易做高。

Figure 2. 64×64 array circuit architecture[5]

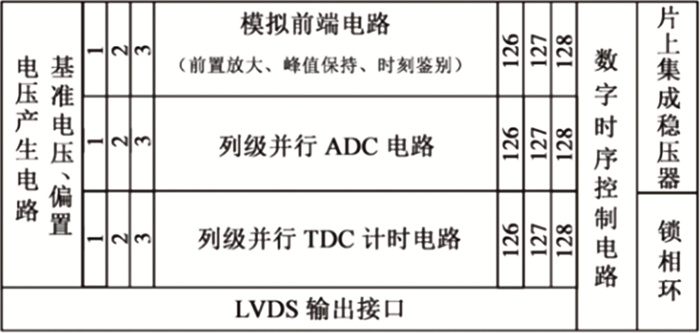

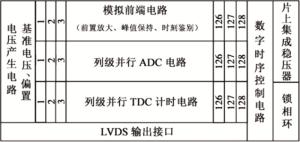

DENG等人提出了一款128×2规模的线性焦平面,其模拟前端包含前置放大器、时刻鉴别电路和峰值保持器,通过TDC计时电路探测时间信息,并采用列级并行ADC电路把强度模拟信号转化成数字信号,电路架构如图 3所示[6]。读出方式根据行帧频不同分为两种,低频下读出电路在同一帧内,完成探测与读出两种操作,高频下采用卷帘方式读出,在第n帧进行探测时,TDC和模数转换(analog-to-digtial, A/D)输出上一帧的时间和强度信息。

Figure 3. 128×2 array readout circuit architecture[6]

上述3种顺序读取型读出电路中,每一个像素单元都有独立的计时模块,使得读出电路阵列像素信息读取灵活、帧频较快,但其缺点是对计时模块的要求较高,电路既要保证计时精度又要保证面积小功耗低。时间驱动型读出电路比前者提高了数据读出的帧频,行列电路结构更为简洁,当到达阵列的回波信号比较稀疏时,部分像素工作,减少了电路功耗。

-

根据线性模式APD焦平面探测器的不同应用场景,目前读出电路有两种读出模式:一是帧频式读出电路,广泛运用于激光雷达系统中;二是异步式读出电路,广泛运用于光学通信[7]。

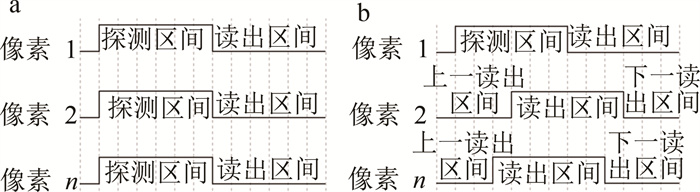

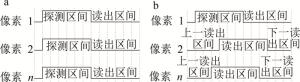

帧频式读出电路工作时间分为探测区间和读出区间,在探测区间内,像素识别回波信号,并在读出区间进行信号读出。帧频式读出电路时序图如图 4a所示,高电平为探测区间,低电平为读出区间,焦平面中所有像素都处于相同工作区间,探测和读出不能同步进行。异步式的读出电路时序图如图 4b所示,每一个像素都保持独立工作,像素内有自己单独的控制时钟。一个阵列里不同的像素可实现探测和读出可同步进行,实现连续实时检测。本文中不讨论异步式读出电路,只讨论帧频式读出电路。

-

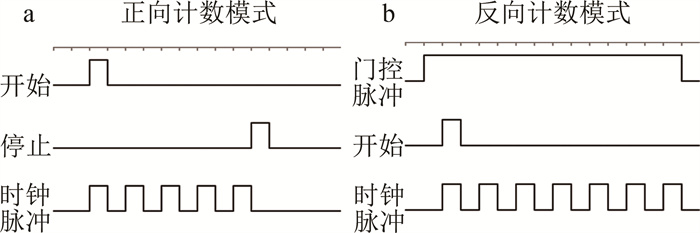

读出电路中计数电路模块有两种计时模式:一是正向计数模式;二是倒向计数模式。正向计数模式的时序图如图 5a所示,激光器发射激光的时刻产生一个开始信号,计数器开始计时,回波信号到达焦平面时产生一个停止信号,计数器停止计时。所有的像素开始计数的时刻相同,停止计数的时刻不同。计数器记录的是光子飞行时间,可根据光子飞行时间计算出探测物体的距离。倒向计数模式的时序图如图 5b所示,存在一个宽度已知的门控脉冲,当回波信号到达时产生开始信号,计数器开始计数,到门控脉冲的下降沿停止计时,每个像素计数器开始计数时刻不同但是停止计数的时刻是相同的。

1.1. 读出电路架构

1.2. 读出电路时序

1.2.1. 读出电路工作模式

1.2.2. 读出电路计时模式

-

回波信号通过APD产生光电流,经过跨阻放大转化为脉冲电压,这个电压脉冲包含了回波的时间信息和光强信息。在时刻鉴别电路模块,使用TDC或者TAC得到时间信息,在峰值保持模块或者全波形输出模块,得到其强度信息[2]。

-

像素单元里,需要将光脉冲信号转化为电压脉冲信号[8],最常见的就是使用跨阻放大器(transimpe-dance amplifier,TIA)。目前比较常见的有电阻型跨阻放大器(resistance transimpedance amplifier,RTIA)、电容型跨阻放大器(capacitive transimpedance amplifier,CTIA)和调节型共源共栅型跨阻放大器(regulated cascode transimpedance amplifier,RGC-TIA)。电容型跨阻放大器常用于宽脉冲电流信号或直流电流探测,跨阻型放大器和RGC型跨阻放大器常用于窄脉冲电流探测。

-

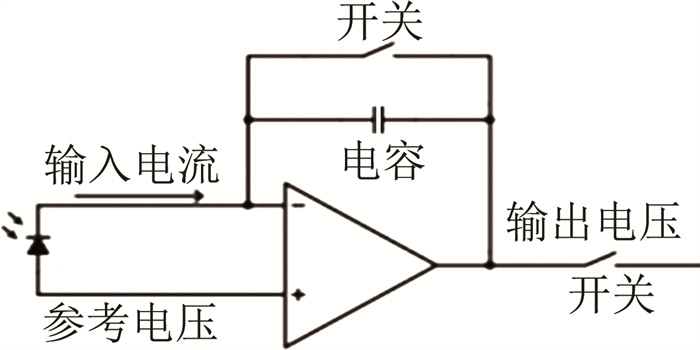

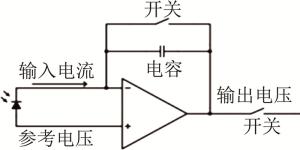

电容型跨阻放大器是常用的输入级,其结构图如图 6所示。此结构的放大器由一个运算放大器和一个积分电容组成。积分电容作为负反馈跨接在运算放大器的负端输入和输出上,形成负反馈回路,该电路本质上是一个积分器,工作时处于积分状态,输入电流向电容充电引起输出端电压变化。探测的光电流脉宽有一定要求,充电时间太短电荷积累较少使得电压变化量较小,不易探测。

DENG等人设计了一种用于64×64规模,AlGaN基底的用于弱光成像的APD阵列读出电路[9]。该读出电路像素采用了电容型跨阻放大器作为输入级,研究了电荷-电压转化因子和积分电容,放大器增益的关系,得到积分电容为70 fF时,放大器的增益为300,最大积分时间约为825 ms,最大可探测光电流为22.8 pA。此探测器探测的直流光电流,为国内学者设计像素电路的跨阻放大器提供了有利的理论支撑。

法国CEA-Leti公司研发的用于闪光激光雷达成像的焦平面[10],使用的跨阻放大器为一个CTIA。此CTIA由一个跨导运算放大器(operational transimpe-dance amplifier,OTA)作为核心放大器,在输出和输入跨接两个大小不同的电容,小电容只有几个fF,以便为快速检测回波提供高增益,大电容可切换提供较大的容量。探测器系统最小可探测100个光子,实现弱光探测。

-

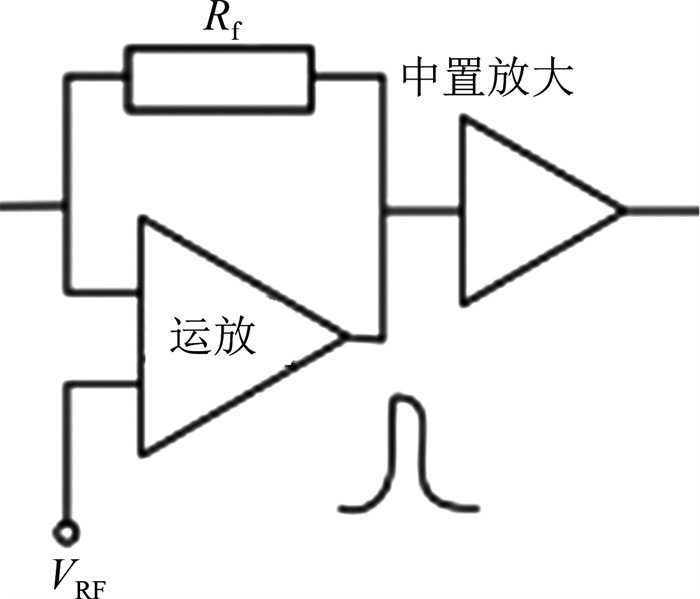

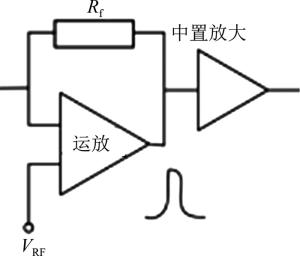

RTIA是将电阻跨接在放大器的负极和输出端口,形成负反馈环路。输入电流值与输出电压值成正比,且比例系数为电阻阻值Rf,通过调整Rf的阻值可实现增益可调的跨阻放大器。DENG在128×2规模的读出电路像素设计中,采用了RTIA做为输入级,将电流脉冲转化成电压脉冲再进行中置放大,前置放大器如图 7所示[6]。此设计中使用了0.11 μm互补金属氧化物半导体(complementary metal oxide semiconductor,COMS) 集成电路工艺,能探测纳秒级脉冲电流,并进行了流片验证,可实现光电流的探测。

Figure 7. Resistance TIA[6]

DRS Techonlogies公司、GEOST公司和Analog Digital Integrated Circuits公司合作为美国航天局用于航天探测的项目设计了一款2×8的基于线性模式的HgCdTe APD单光子探测器的读出电路[11]。输入级采用的也是RTIA,使用的Rf为可变电阻,阻值181 kΩ~500 kΩ可调;整体的读出电路信噪比大于10 dB的时候可以完成单光子检测,光子探测效率达到50%。2021年,这个焦平面已运用在美国国家航空航天局(National Aeronautics and Space Administration,NASA)专门为小行星体的任务而设计的一种新型空间激光雷达中,用于地形测绘和支持样品采集或着陆[12]。

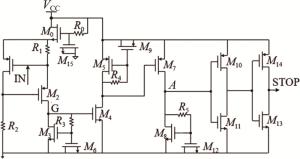

另一种常见的输入级是RGC-TIA。BAI等人[4]基于大面阵InGaAs基背照工作的线性模式APD芯片,设计了规模为32×32的读出电路的架构和像素单元电路结构;像素的前置放大器是由RGC-TIA输入级级联的两级自偏置共源级单级放大器组成的,其电路图如图 8所示。在400 MHz下增益可以达到110 dB,等效输入噪声电流有效值约200 nA,噪声电流峰值为1.32 μA;前置放大器可以实现5 μA、脉宽2.45 ns的窄脉宽弱光电流的检测。

Figure 8. Regulated cascode TIA[4]

电容型跨阻放大器相当于一个积分器,可以提供较低噪声,且线性度很好,但是同工艺下的面积和功耗相对于其它跨阻放大器会更大。电阻型跨阻放大器的增益由反馈电阻决定,可通过调节反馈电阻阻值调节增益值。RGC-TIA可以很好地隔离前级光敏芯片的结电容,但是为了降低噪声应增加电路内晶体管的跨导,会导致面积与功耗的增加。三者常见的输入级都有各自的优缺点,在电路设计中,综合增益、带宽以及等效输入噪声的指标要求来进行选择。前置放大输入电路还有直接注入型、电流镜型等,在此不进行更多讨论。

-

读出电路探测强度信息的方式也有很多种,比较常见的是采样保持输出、峰值保持输出和全波形采样输出。

ZHANG等人[13]针对线性模式下的128×128规模HgCdTe APD探测器,设计了后续的读出电路。像素单元的架构如图 9a所示,前置放大器CTIA的输出节点连接到保持采样保持模块,并保持常开模式对节点电压进行实时监控;电路时序图如图 9b所示,CTIA输出节点P点电压通过采样保持模块实时输出V2d。此电路采用SMIC 0.18 μm 1P6M CMOS工艺进行设计和流片。

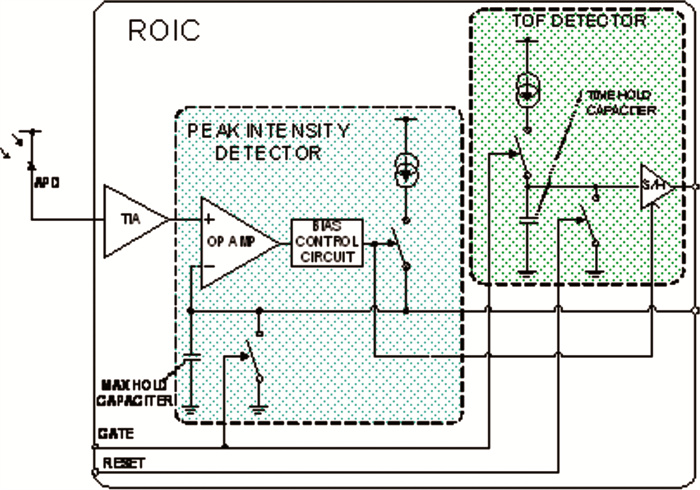

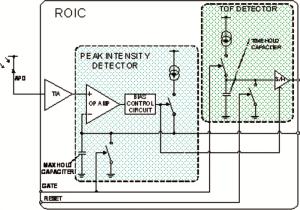

峰值保持电路也是一种常见的获取回波的强度信息的方法。日本三菱公司[14]设计了一款用于3维成像的InAlAs的APD阵列探测器读出电路,采用0.18 μm的SiGe-BiCMOS工艺制备。像素单元框架图如图 10所示,像素包含跨阻放大器、峰值强度检测电路和光子飞行时间检测模块。峰值检测模块中,每当输入信号电压大于上一时刻存储在MAXHOLD电容上最大电压时,会触发开关输出一个晶体管-晶体管逻辑电平(transistor transistor logic,TTL)的逻辑高电平。瞬间,通过用电流源对MAXHOLD电容充电,最大电压被刷新。GATE信号保持高电平,MAXHOLD电容上电压持续刷新,直至检测到峰值强度。但是峰值检测模块中开环放大器增益有限,检测小信号时候,输出的电压可能会低于TTL逻辑电平,使得检测无法正常进行。通过加入一个偏置调节电路,使得运算放大器的输出略低于偏置控制电路也能正常工作实现检测峰值的目标。

Figure 10. Pixel circuit framework[14]

日本三菱公司这款探测器将读出电路和1维快速扫面设备连接,可以获得实时的3维范围图像,但是使用的是线列组成的阵列,电路集成度不高,会产生阵列无法进一步扩大的问题,帧率也因为多路选通电路无法进一步提高。

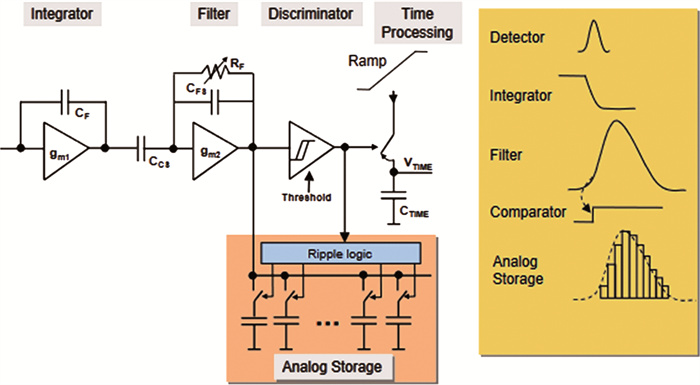

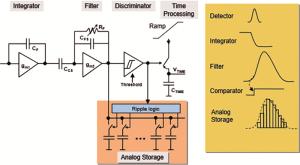

探测回波信号强度信息的方法还有使用包络采样的方法,输出为整个电压脉冲信号的全波形,其中包括了脉冲上升时间、脉冲下降时间、脉宽和峰值强度等信息。JOHNSON等人设计了一个64×64阵列规模的读出电路,图 11是单元像素的设计[15]。探测的光电流经过积分器和滤波器转化为电压脉冲,检测到回波到达时,开启波形采样。将瞬时的波形电压存储在多个电容上,全波形包络采样保留回波信号的脉宽峰值电压等信息。

Figure 11. Pixel circuit framework using sampling[15]

-

在像素内部常见的计时方式有两种:将光子飞行时间转化成数字信号进行输出的TDC和将其转化为模拟信号的TAC[16]。在同样的工艺下,TAC的面积会比TDC小,但是TDC直接输出的是数字信号,抗干扰能力更强。

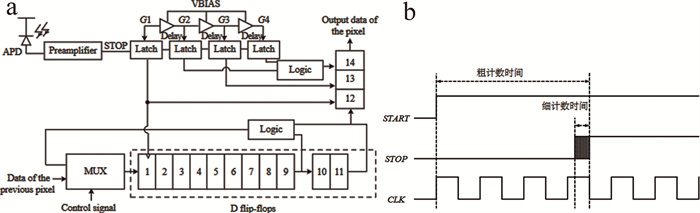

2018年,LI等人设计了一款64×64阵列[17],用于3维成像的InGaAs/InP激光焦平面探测器。光子飞行时间的探测采用了二段式TDC,保证了测量范围和测量的时间精度。读出电路主要是由外围电路、驱动电路和像素阵列等组成。像素单元里包括了放大模块和14位计数器,其中10位主计数器分辨率是8 ns,4位辅助计数器采用4相时钟技术将分辨率提高到1 ns,像素级TDC电路图如图 12a所示;计数器时序图如图 12b所示。start信号开始时,主计数器开始计数直到stop信号来临,停止计数。但是因为无法确定CLK边沿与stop上升沿时间差,为了减小误差引入辅位计数器进行细计数,stop信号来开始细计数。最后使用计数时间减去细计数时间得到误差较小的光子飞行时间。探测器探测距离为1 km,距离分辨率为15 cm,TDC的最小时间分辨率为1 ns。

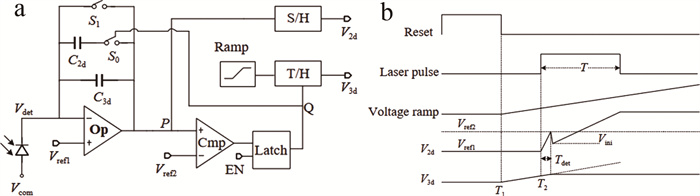

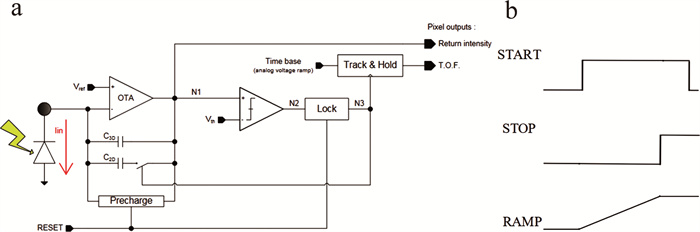

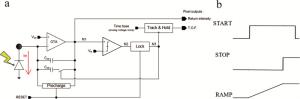

CEA-Leti公司开发了一种新型320×256规模的混合焦平面阵列[10],可以在被动和主动两种模式下运行。在被动模式下,它可以作为一个传统的2-D热成像仪使用;在主动模式下,它可以作为一个闪光激光雷达成像仪使用,其阵列中每个像素电路都能探测回波信号的时间信息和强度信息。像素单元架构如图 13a所示,此设计采用的是TAC的计时方法;时序如图 13b所示,光子发出时给Track&Hold模块输入一个基准斜坡电压,光电流输入CTIA之后C3D上开始积累电荷,电容上的电压上升。小电容上电压到达阈值电压后,比较器翻转输出高电平作为stop信号,锁存Track&Hold模块,并输出此刻斜坡电压值。输出的模拟斜坡采样电压值,可以根据推入Track&Hold模块的基准斜坡电压得到光子飞行时间。读出电路测距距离达到30 m,精度达到30 cm,TAC的最小时间分辨率为2 ns。

传统TAC易受到温度等外界因素的干扰,限制了其精度,同时TAC的精度与测量范围相矛盾,测量精度越大,斜坡电压斜率越大,测量范围越小;测量精度越小,斜坡电压斜率越小,测量范围越大[18]。随着3维成像所需清晰度的增加,所需要的像素点也增加,阵列规模变大。但是采用同样的工艺下,单个TDC的面积远大于TAC,面积较大的模块在大阵列焦平面探测器中是不利的。需要根据时间测量精度和面积功耗来折中选择和设计TAC和TDC[19]。

-

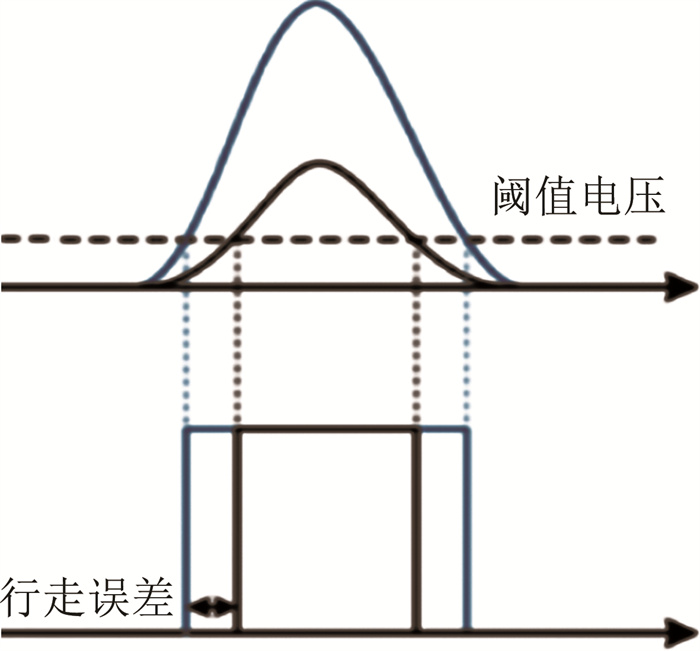

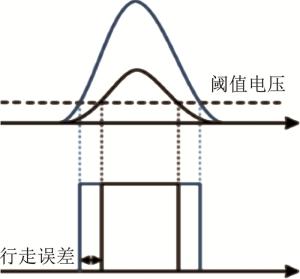

在读出电路设计中,精确测量回波信号到达的时刻是一个难题,它直接影响了整个探测器的精度。为了记录光子到达的stop信号,大多数像素内部采用了单阈值前沿时刻鉴别器,但是由于光电流脉冲的幅度不一致,会导致时间行走误差,如图 14所示,它最大可达到脉冲上升时间的一半。下面将介绍几种减小行走误差的方法,并对其进行详细分析。

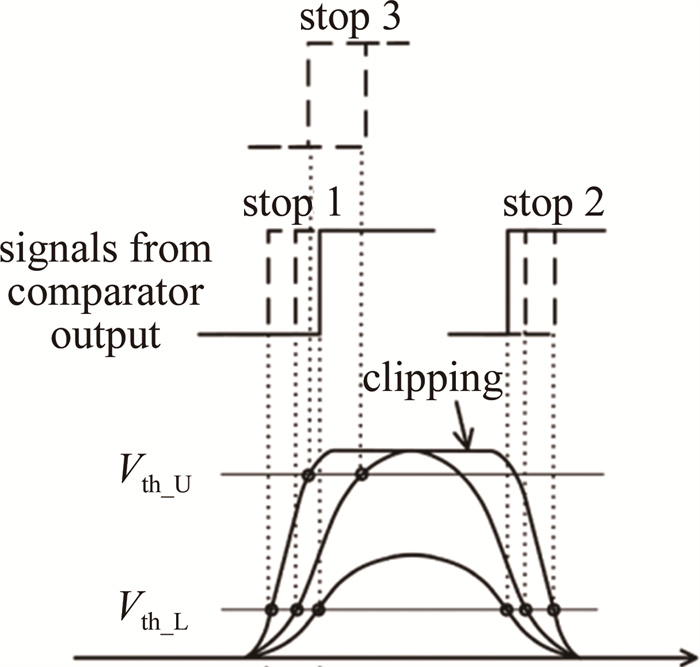

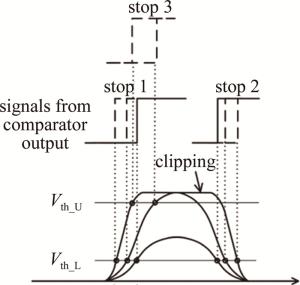

KURTTI等人[20]提出了一种基于双阈值方法的激光脉冲到达信息的检测模块的电路设计,原理如图 15所示。使用两个高性能比较器提供一个较低的阈值70 mV和一个较高的900 mV阈值。设置较低的阈值的比较器得出stop1信号和stop2信号,设置较高的阈值的比较器得出stop3信号。通过3个stop信号可以估计出脉冲宽度和脉冲上升时间。后续通过实验采集得到不同的脉冲强度及不同的输入电流对应的不同大小的行走误差,构建出脉冲宽度和上升时间的行走误差补偿曲线。这两种情况下都使用了线性插值来实现连续的补偿曲线,并通过这些补偿曲线进行补偿。采用了0.35 μm COMS的工艺,整体电路的行走误差在25 ps左右。

Figure 15. Schematic diagram of the double threshold method[20]

通过实验采集得到的行走误差补偿曲线,如图 16a和图 16b所示。图 16a显示了在整个振幅范围内包含80个测量点,1 ∶100000的动态范围内,行走误差和测量脉冲宽度的函数,而图 16b显示了在包含46个振幅点,100 ∶100000的动态范围内,行走误差和测量时间间隔的函数。这两种情况下都使用了线性插值来实现连续的补偿曲线。补偿曲线被存储在查找表中,并通过这些表进行查找补偿。

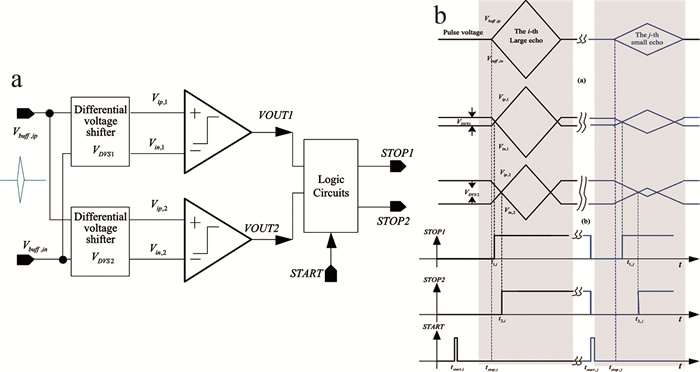

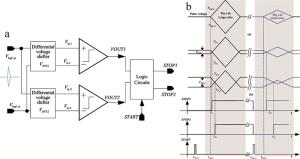

ZENG等人提出了一种用于光子飞行时间(time of flight,TOF)的大动态范围的接收器[21],回波信号鉴别使用的差分电压位移定时鉴别方案,此方法的电路框架如图 17a所示。将从TIA传出的电压脉冲信号转化成一个差分信号,在提供给个差分信号不同的共模电平,使其产生交叠,输入的两对差分信号提供的共模信号的差值满足VDVS2=2VDVS1,且共模电平VDVS1设置为50 mV,VDVS2设置为100 mV;再将两对差分信号输入到两个比较器中得出交叠时间t1和t2,推出Tstop=2t1-t2,时刻鉴别模块的时序图如图 17b所示。电路采用0.18 μm CMOS工艺,最小探测电流信号为0.28 μA,行走误差约为1 ns。

无论是构建补偿曲线还是用交叠时间去确定到达时刻,这些方案都可以放在线性APD焦平面读出电路的像素单元作为时刻鉴别模块。传统的单阈值前沿时刻鉴别缺点主要在于:因回波信号的脉宽不确定,会引入一个最大值可达一半的上升时间的行走误差,想要提高时刻鉴别精度就需要提高比较器性能,这对于电路设计是一个不小的挑战。单阈值方法的优点也比较明显:只需要一个比较器,在大阵列中可以节约一定面积和减少一定功耗。相较于传统的单阈值方法,双阈值方案有极大地减小行走误差的优点,提高了时刻鉴别的准确度,但是会增大像素面积和功耗,这对大阵列的读出电路性能指标影响较大。表 1是一些参考文献中读出电路的主要指标对比。

参考文献 工艺 阵列 TIA TDC/TAC 像素尺寸/μm 探测范围 时间分辨率/ns 距离分辨率/cm [4] 0.35 μm CMOS 32×32 RGC,110 dB@400 MHz TDC 150 — 2 30 [6] 0.11 μm COMS 2×128 RTIA TDC — 0.84 km~4.8 km 0.5 7.5 [10] 0.18 μm CMOS 320×256 CTIA TAC 30 30 m 2 30 [12] — 2×8 RTIA增益带宽积: 3×1013 TAC — — — — [13] 0.18 μm CMOS 128×128 CTIA, 62 dB TAC 50 — — — [14] — 256×256 — TAC — — — — [17] — 64×64 RGC TDC 150 1 km 1 15 Table 1. Comparison of readout circuit indicators

传统TAC时间测量精度和测量范围只能折中选择,而TDC能达到高精度的同时增加位数实现增加测量范围。TAC输出的是模拟信号,TDC输出的是数字信号,TAC的模拟信号需要ADC转化成数字信号读出,而TDC可直接输出,抗干扰能力更强,但TDC的高频时钟会给其它模拟模块造成时钟串扰,同时大规模全局时钟同步实现也较为困难。随着3维成像对清晰度的要求提高,像素点的数量也相应增加,导致阵列规模扩大。然而,在相同的工艺条件下,单个TDC的面积远远超过TAC,这对大阵列焦平面探测器是不利的,如法国公司推出的320×256规模的大阵列读出电路使用的依然是TAC。因此,TAC和TDC的选择需要在时间测量精度、测量范围、面积和功耗之间进行权衡和优化设计。

国外对线性APD的研究持续时间久且技术成熟度高,逐步趋向大规模读出电路和大阵列、低功耗、超长探测距离、高精度和高速成像等方向发展。国内研究相对落后,尤其是在读出电路的设计方面,随着激光雷达的兴起,因其具有广阔的应用前景,近年来国内一些企业、高校和研究所加大了对线性焦平面读出电路的研究力度。

2.1. 跨阻放大电路

2.1.1. 宽脉冲电流探测

2.1.2. 窄脉冲电流探测

2.2. 强度信息模块

2.3. 时间信息模块

2.3.1. TDC和TAC

2.3.2. 时刻鉴别电路

-

按工作模式,线性模式APD读出电路在可划分为帧频式和异步式。帧频式中所有像素采用相同的时钟,在1帧内读出所有像素输出。异步式中每个像素都有独立的时钟,可以实现读出和探测同时进行、连续探测。按数据读取方式,读出电路分为顺序存取型和事件驱动型。顺序存取型按照时钟周期、按顺序逐个读取或者串行读取,本文中列举了3个已有的设计。时间驱动型是通过检测到回波信号后,产生数字信号,并申请占用读出通道,然后进行读出数据,本文中未举例说明。

参考文献[4]中提到的读出电路架构将光子飞行时间转换为数字信号,通过逻辑控制将每一行的32个计数器串联起来,再进行串行输出,可以有效地减少读出时间,但暂时没有保留强度信息。参考文献[5]中将光子飞行时间转化成模拟电压,再储存在像素内的电容上,通过行选和列选,逐个读出像素内的电压值,因此成像帧率受限。参考文献[6]中采用并行ADC将强度信息的模拟电压转化为数字信号,光子飞行时间也转化为数字信号进行读出,但是这样采用列级ADC规模会使得读出电路芯片面积大大增大。

线性模式APD读出电路的关键模块电路设计难点有两个方面:一是如何捕捉微小回波信息,这需要光电检测接口的跨阻放大器具有高增益、高信噪比;二是如何捕捉回波信息的时刻信息,这涉及到时刻鉴别的方法和精度。传统的单阈值鉴别会导致较大的行走误差,最大可达到脉冲宽度的一半,因此使用不同的时刻鉴别方案减少行走误差是未来研究的重要方向。保留强度信息有3种方法:(a)采用实时采样,输出积分器电压;(b)采用峰值保持电路获得脉冲电压最大值;(c)采用包络采样,将脉冲电压信息存储在采样电容里,得到脉宽和强度等信息。

为了满足各种运用需求,如自动驾驶汽车、无人机驾驶、制导等,3维成像正朝着高精度、大范围测量的方向发展。用于3维成像的线性焦平面APD探测器为了满足高精度的需求,APD阵列趋向于大阵列规模,增加像素、高灵敏度、探测微小回波信号、多维度探测,从光子飞行时间测距到同时保留回波强度。相应的,读出电路也朝着大规模阵列、低噪声弱电流检测、时间强度全波形探测等多功能的方向发展。

Map

Map

DownLoad:

DownLoad: