Design of improved pixel sharing CTIA infrared readout circuit based on bandgap reference

-

摘要:

为了提高红外读出电路动态范围、增强红外成像质量,加入暗电流抑制模块电路,设计了一种四像元分时共享的电容反馈跨阻放大器(CTIA)和带隙基准源相互配合的高性能红外读出电路。通过带隙基准源产生两个基准电压586 mV和293 mV,其中293 mV基准电压值的温漂系数达到1.49×10-6/℃,可对分流管的栅极和源极提供稳定的电压偏置,实现对暗电流的精准撇除。结果表明,该电路可实现电流信号从10 pA~10 nA宽动态范围的积分电压读出,读出数据通过线性拟合,拟合优度R2达到0.9992,说明电路性能良好。此研究未来可应用到线列和面阵的红外探测器中。

Abstract:In order to improve the dynamic range of the infrared readout circuit and enhance the quality of infrared imaging, a high-performance infrared readout circuit with a four-pixel time-sharing capacitive feedback transimpedance amplifier (CTIA) and a bandgap reference source was designed by adding a dark current suppression module circuit. Two reference voltages of 586 mV and 293 mV were generated by bandgap reference source. Among them, the temperature drift coefficient of the reference voltage value of 293 mV reaches 1.49×10-6/℃, which can provide stable voltage bias for the gate and source of the shunt tube to achieve accurate skim of the dark current. The results show that a wide dynamic range of integral voltage readout of current signals from 10 pA to 10 nA can be realized, and the readout data are fitted by a linear fit with a goodness of fit (R2) of 0.9992, which indicates that the circuit performs well. This study can be applied in the future to linear array and focal plane array infrared detectors.

-

Keywords:

- detectors /

- readout circuit /

- dark current suppression /

- pixel sharing /

- bandgap reference

-

0. 引言

半导体红外探测器目前在军事和民用领域都有多种应用场景,其重要性不言而喻。其中,探测器的主要核心部件为红外焦平面阵列组件[1-2],该组件由红外感光阵列和读出电路(readout integrated circuit,ROIC)构成,红外探测器接收到的红外辐射能量通过感光阵列实现光辐射信号向电流信号的转换,但由于产生的信号十分微弱,需要进一步通过读出电路进行处理[3]。伴随着越来越多应用场景日渐增长的需求,红外焦平面的分辨率也朝着更高发展,而分辨率的提高直接决定了感光阵列规模增加,像元面积减小;像元面积的减小则直接影响了ROIC设计时的电容面积。因此,很难让感光电流在小像元面积内的电容上积分更多的电荷,最大非饱和输入信号转化成积分电压受限;同时暗电流影响着最小可输入信号的大小,导致现有读出电路的动态范围降低,而低动态范围会减弱红外系统的精度,最终影响红外图像质量[4-7]。因此,在设计红外读出电路时,设计者应尽可能地去提高电路的动态范围以保证准确地读出红外数据[8-10]。

为满足红外探测器发展需求,在有限的像元面积中实现更高的电荷容量和降低暗电流的影响,在读出数据时,本文中采用相邻的多个像元划分时间间隔地共享一个积分电容来节省面积,从而提高电荷容量。电路输入级结构采用电容反馈跨阻放大器(capacitive feedback transimpedance amplifier,CTIA),它具备众多优点,例如:(a)提高放大器增益,实现高注入效率;(b)小积分电容基于密勒效应实现等效大电容的效果;(c)运放虚短虚断特性可以给探测器两端提供稳定的偏置电压,抑制产生正向导通电流等优点[11-12]。探测器未对物体进行探测时,只接收背景辐射,会产生背景电流,同时探测器因自身材料缺陷原因会产生暗电流。进行探测时产生的总电流为光电流、背景电流以及暗电流的和[13-14]。因此,增加背景抑制电路,通过带隙基准源产生两个基准电压对分流管进行偏置,基准电压都具有很高的稳定性和精度,降低积分信号中背景电流和暗电流的信号分量,增大积分时间来提高有效动态范围。

1. 电路原理分析

1.1 带隙基准源基本原理

基准电压通过对温度系数为正、负两种极性的电压Vp和Vn相加而产生,且二者对应不同的权重系数K1和K2。K1和K2的值通过Vp和Vn对其温度T求导后二者相加为零来确定,从而产生零温度系数基准电压值,如图 1所示。

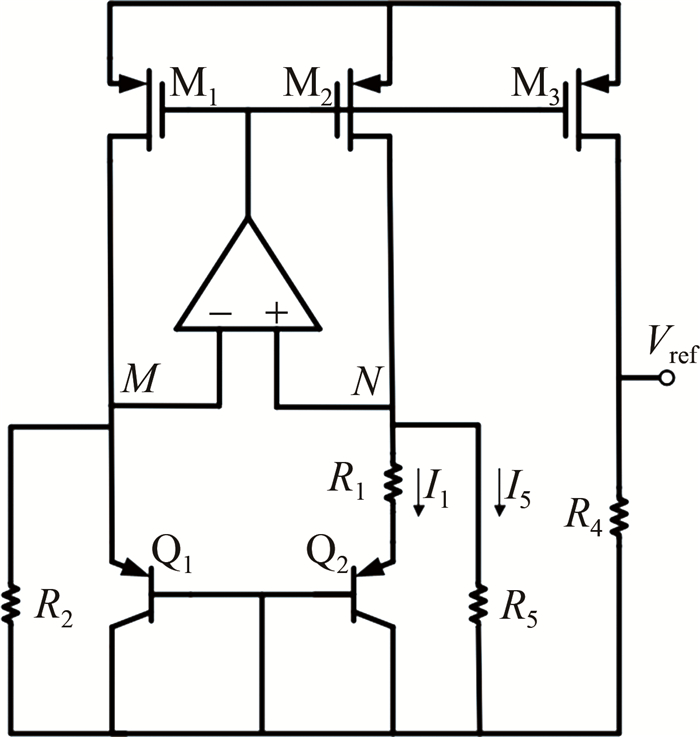

图 2为传统的1阶补偿带隙基准电路结构图。图中,PNP三极管Q2的面积是Q1的n倍,M1~M3为尺寸相同的电流镜,电阻R2和R5阻值相同。M和N点通过运放钳位的作用使之电位相同,由VEB, 1=VEB, 2+I1R1,可得I1=R1-1VTln n,其中:VEB, 1为晶体管Q1的发射极和基极间的电压;VEB, 2为晶体管Q2的发射极和基极间的电压;VT为热电压。该电流与温度成正比,为正温度系数电流,流过电阻R5的电流I5=VEB, 1/R5,该电流为负温度系数电流[15-17]。二者之和通过M3镜像流过电阻R4形成基准电压Vref输出,表达式为[18]:

Vref =R4R5VEB,1+R4R1VTlnn (1) 为了产生在一定工作温度区间内无变化的所需要基准电压值Vref,可通过改变电阻R4与R5和R1的比例关系,但晶体管的基极和发射极间的电压VBE并不是和温度成线性比例的,其温度特性的表达式为[19]:

VBE(T)=Vg(T)−[Vg(T0)−VBE(T0)]×TT0−(η−α)VTlnTT0 (2) 式中:T为系统温度;T0为自我选择的参考温度;Vg(T)、Vg(T0)分别为带隙在温度T和温度T0时的带隙电压;η为与双极性晶体管相关的常数;α为与电压VBE上电流有关的常数。

因此,需要增加高阶温度补偿电路进一步降低温漂系数,获得性能更高的带隙基准源。

1.2 CTIA的基本原理

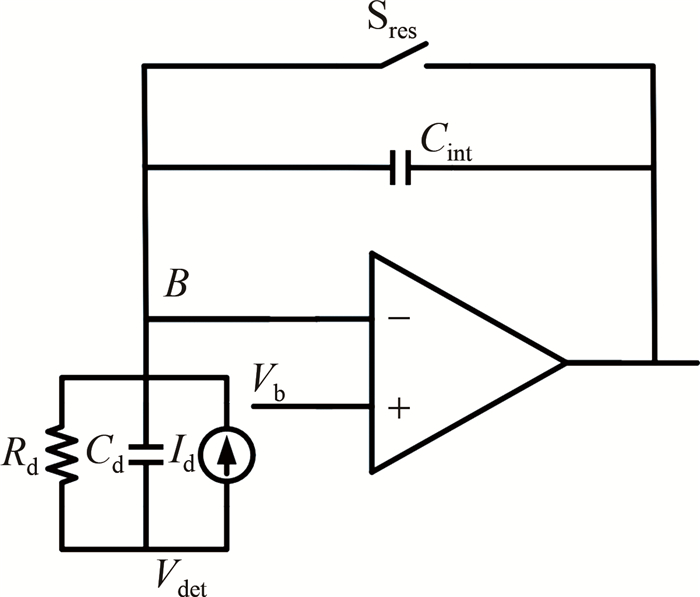

图 3为CTIA电路结构等效模型图。探测器由电阻Rd、电流源Id与电容Cd等效组成,复位开关Sres在受时钟信号的控制下红外感应电流Id流入到积分电容Cint上,从而在Cint上完成对红外感应电流的电压转换[20-22]。

当Sres闭合时,CTIA电路处于复位状态,放大器输出端和负向输入端B点短接,积分电容Cint两端变为短接状态,电位达到一致。并且由于放大器中存在虚短特性,使B端电压等于正向输入端Vb的电压,因此当感光电流流入CTIA电路时,Vb为积分的起始电压。但是由于在实际设计过程中,放大器的增益不是理想状态,并不是无限大。因此,复位时的放大器输出端电压值为[13]:

Vout =AA+1Vb (3) 式中:A为直流开环增益;Vb为放大器正向输入端电压。当Sres断开时,CTIA电路处于积分状态,积分电容Cint在放大器的反馈回路中。输出电压此时从式(3)中的值开始积分,相比较理想状态下的积分电压增加了Vb/(A+1),积分完成后的输出电压为[13]:

Vout =A(A+2)(A+1)2Vb+AA+1I×tCint (4) 式中:I为红外感应电流;t为积分时间。由式(4)可知,用于CTIA输入级结构中的运算放大器,设计时要考虑尽可能地提高直流开环增益来保证其放大器的输入端“虚地”,以提高对红外微弱信号的积分精度。

2. 总体电路设计和仿真结果

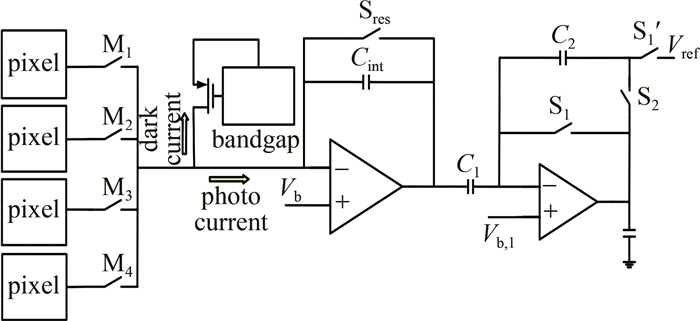

本文中所设计的读出电路由像元导通开关、暗电流抑制模块、带隙基准电路、CTIA输入级以及相关双采样(correlated double sampling,CDS)电路组成,如图 4所示。图中由带隙基准电路产生的两个基准电压分别与分流管的栅极和源极相连,并提供稳定的偏置电压,使其精准减除暗电流。CTIA输入级由高增益放大器和积分电容组成,而高增益放大器可获得高注入效率。CTIA电路对于探测器由光电转换的电流积分完成后,转化后的电压信号通过CDS电路输出,最终完成对红外探测器的感光阵列产生的微弱电流信号的处理。

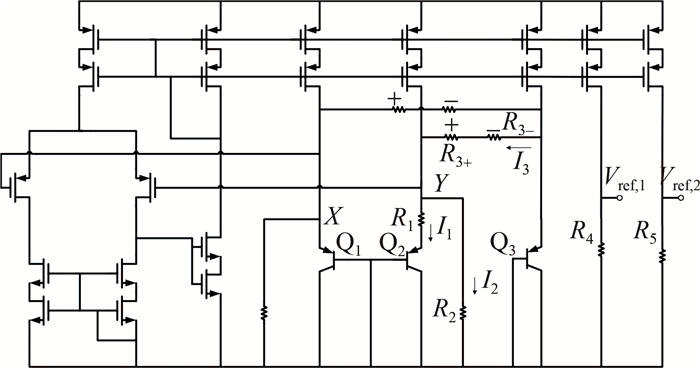

本设计中采用的带隙基准电路核心部分如图 5所示。通过高阶温度补偿的方式,双极型晶体管Q3和电阻R3组成的回路进行温度校准,以提高基准电压稳定性。在精准镜像电流方面,电流镜的部分采用共源共栅的电路结构来降低沟道调制效应影响,提高电流精度,并通过在极性不同(随温度变化)的两种电阻R3+和R3-在高阶温度补偿回路中精准调控,R3+是电阻率随着温度升高而增加,而R3-恰好相反。根据红外材料所产生的暗电流量级,完成两个基准电压值Vref, 1=293 mV和Vref, 2=586 mV的输出,从而和分流金属氧化物半导体型场效应管(metal-oxide semiconductor field-effect transistor,MOSFET)相连,实现暗电流精准减除。

Vref, 1和Vref, 2的表达式如下所示:

Vref,1=R4R2[VEB,1+(R2R1lnn)VT+R2R3ln(TT0)VT] (5) Vref,2=R5R2[VEB,1+(R2R1lnn)VT+R2R3ln(TT0)VT] (6) 式中:R3=R3++R3-。

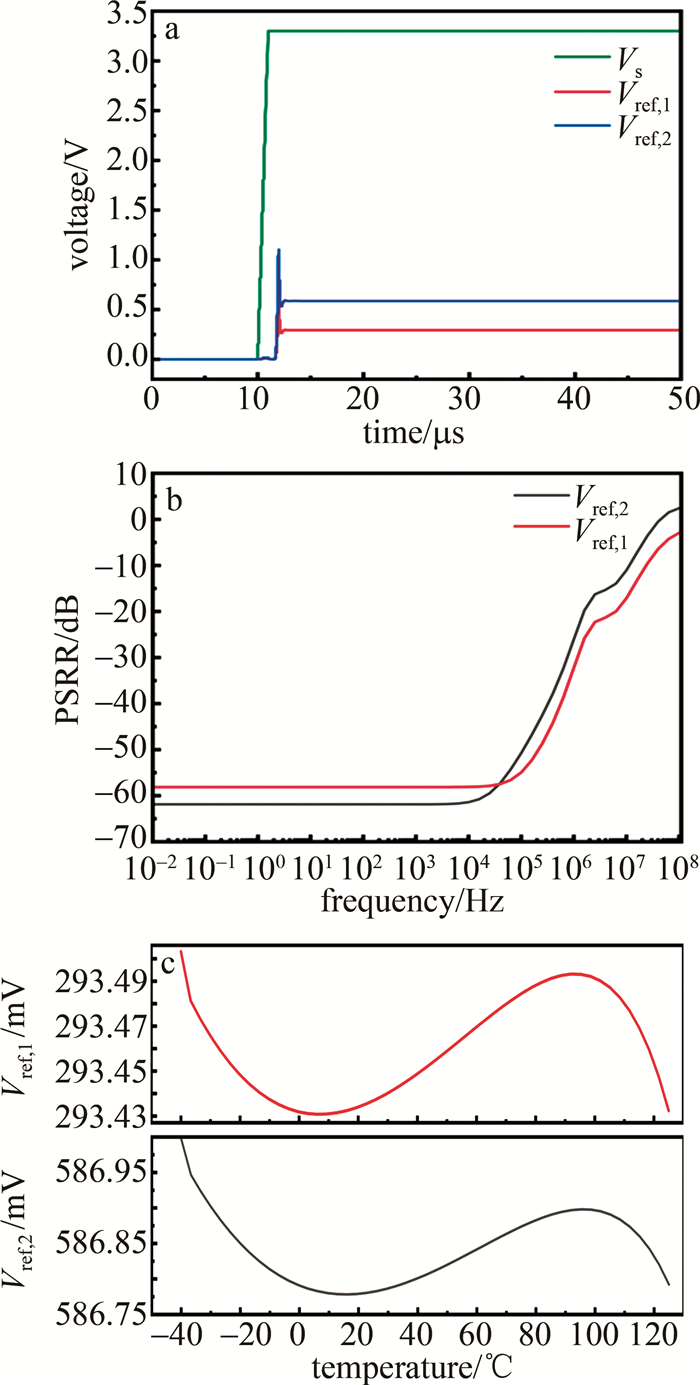

带隙基准电压电路的主要性能指标在tt工艺角下进行仿真测试,图 6是瞬时启动仿真、电源抑制比(power supply rejection ratio,PSRR)以及基准输出电压的曲线图。如图 6a所示,设置仿真条件:电源电压Vs从0 V变化至3.3 V,结果表明,在上电完成后基准电压Vref, 1和Vref, 2可以正常输出工作。图 6b中Vref, 1和Vref, 2的电源抑制比分别达到62 dB和58 dB,并通过图 6c中的基准电压曲线计算可得两条基准电压的基准温度系数分别达到1.49×10-6/℃和2.46×10-6/℃,性能良好。

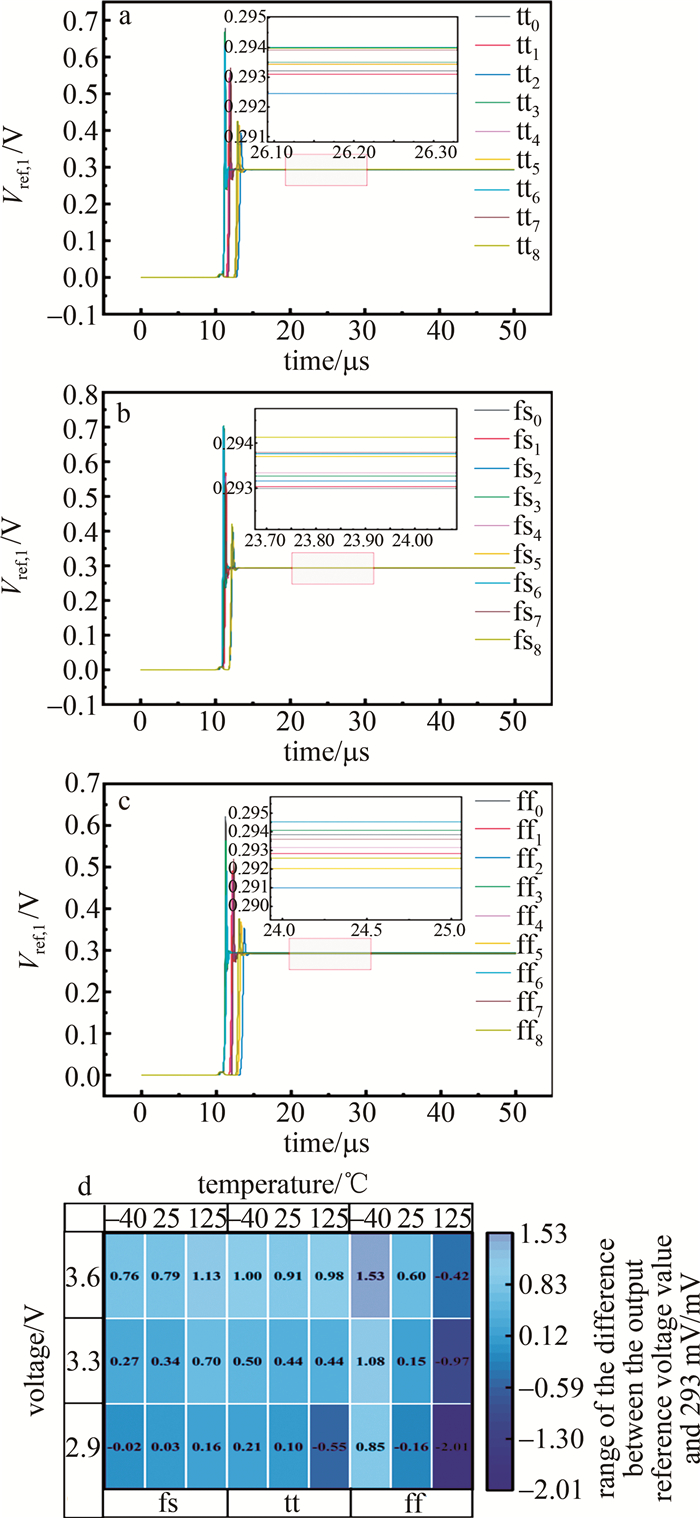

进一步通过不同的工艺角、不同的电源电压以及不同的温度值相互组合,形成对带隙基准电路中两个基准电压的多个仿真测试条件。测试条件为:温度-40 ℃、25 ℃、125 ℃;电压2.9 V、3.3 V、3.6 V;工艺角tt、ff、fs。详细的参数设置如表 1所示。

表 1 不同工艺角、温度、电压下的组合测试参数表Table 1. Combined test parameters under different process angles, temperatures and voltagestt/ff/fs 0 1 2 3 4 5 6 7 8 temperture/℃ -40 25 125 -40 25 125 -40 25 125 voltage/V 2.9 2.9 2.9 3.3 3.3 3.3 3.6 3.6 3.6 图 7a、图 7b、图 7c分别是基准电压Vref, 1按照上述表 1中的温度、电压参数组合在不同工艺角tt、ff、fs下进行的仿真测试结果图,并通过输出值和基准电压的差值做了误差分析图,如图 7d所示。基准电压Vref, 1受到温度、工艺和电源电压的波动影响,最大误差达到2 mV,表明输出基准电压值具有很高的稳定性。

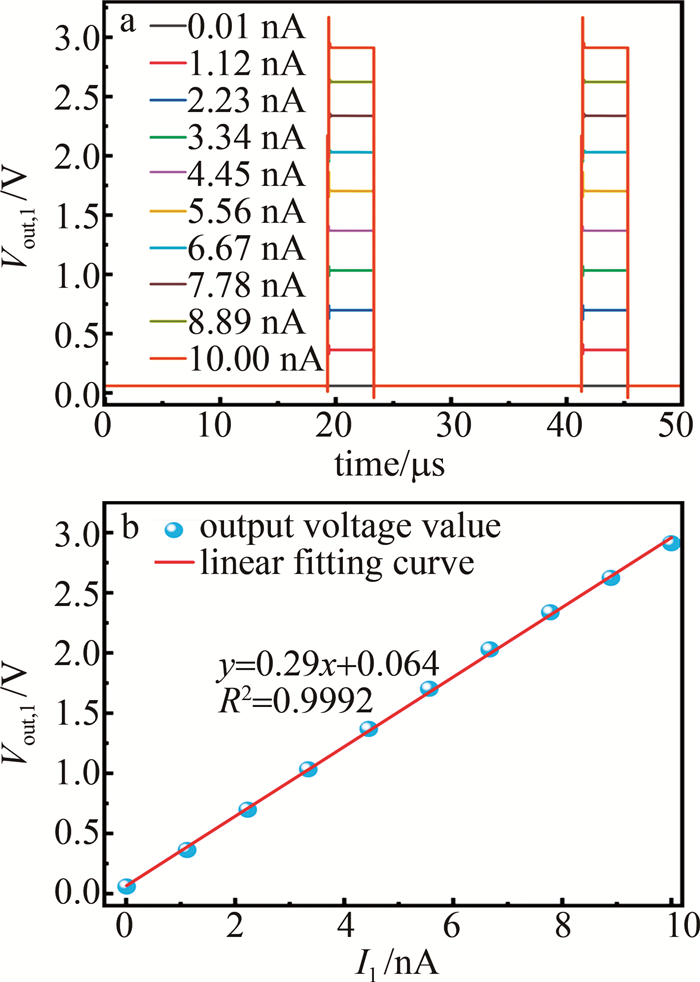

通过带隙基准源电路对分流管的栅极和源极进行偏置,同时对整体电路中单个像元通路进行仿真测试,设置探测器单个像元的积分电流I1在10 pA~10 nA的范围内,此积分电流是去除暗电流值后的值(下同),仿真结果测试如图 8所示。通过CDS电路输出的电压值Vout, 1具有很高的线性度,并且数据通过线性拟合后,拟合优度R2达到0.9992,电路性能良好,能够实现对10 pA~10 nA宽动态范围的电流积分并读取积分电压值。

测试整体电路性能,分别设置4个像元的积分电流值为0.8 nA、2.8 nA、4.8 nA、6.8 nA,并通过时序电路控制通道开关。最终,经CDS电路输出的四通道电压值分别为0.3238 V、0.9398 V、1.5957 V、2.2515 V,和单通道像元测试基本吻合,所设计的改进型分时共享红外读出电路结构工作可行。

3. 结论

通过高阶温度补偿的带隙基准电路给分流MOSFET管的栅极和漏极进行稳定偏置的方法,对暗电流进行抑制,减小积分电容的面积;同时采用多路分时共享的CTIA输入级读出架构,等效增大了像元设计面积,降低了读出电路的设计难度。仿真结果表明,通过二者结合后,实现了对积分电流从10 pA~10 nA的宽动态范围电压读出,并且线性拟合后R2的数值达到0.9992,具有良好的线性度和动态范围。但由于整体电路中采用多路开关,开关中的电荷注入效应会导致读出线性度有所降低,在此方面还需进一步改进和优化。未来可应用到线列和面阵规模的红外探测器当中。

-

表 1 不同工艺角、温度、电压下的组合测试参数表

Table 1 Combined test parameters under different process angles, temperatures and voltages

tt/ff/fs 0 1 2 3 4 5 6 7 8 temperture/℃ -40 25 125 -40 25 125 -40 25 125 voltage/V 2.9 2.9 2.9 3.3 3.3 3.3 3.6 3.6 3.6 -

[1] ZHOU J J, ZHANG Y C, LU W G, et al. A low power readout circuit for 640×512 IRFPA with dynamic windowing readout[C]// IEEE International Conference on Electron Devices & Solid-state Circuits. New York, USA: IEEE Press, 2015: 1-2.

[2] 王欣. 红外焦平面阵列探测器的研究进展[J]. 舰船电子工程, 2020, 40(9): 157-161. DOI: 10.3969/j.issn.1672-9730.2020.09.038 WANG X. Research progress of infrared focal plane array detector[J]. Ship Electronic Engineering, 2020, 40(9): 157-161(in Ch-inese). DOI: 10.3969/j.issn.1672-9730.2020.09.038

[3] 郝立超. 甚长波红外探测器信号读出电路结构研究[D]. 上海: 中国科学院研究生院(上海技术物理研究所), 2014: 3-29. HAO L Ch. Research of readout integrated circuit for VLWIR FPAs[D]. Shanghai: Graduate University of Chinese Academy of Sciences(Shanghai Institute of Technical Physics), 2014: 3-29 (in Ch-inese).

[4] 白丕绩, 姚立斌. 第三代红外焦平面探测器读出电路[J]. 红外技术, 2015, 37(2): 89-96. BAI P J, YAO L B. Read out integrated circuit for third-generation infrared focal plane detector[J]. Infrared Technology, 2015, 37(2): 89-96(in Chinese).

[5] CANNATA R F, HANSEN R J, COSTELLO A N, et al. Very wide dynamic range SWIR sensors for very low background applications[C]// Infrared Technology and Applications Ⅹ Ⅹ Ⅴ. Orlando, Florida, USA: SPIE Press, 1999: 756-765.

[6] 颜伟军. 宽动态范围的红外焦平面读出电路设计[D]. 南京: 东南大学, 2020: 2-19. YAN W J. Design of the infrared focal planereadout integrated circuit withhigh dynamic range[D]. Nanjing: Southeast University, 2020: 2-19(in Chinese).

[7] 岳冬青, 马静, 李敬国, 等. 高光谱用长波红外探测器读出电路设计[J]. 激光与红外, 2019, 49(8): 1014-1018. DOI: 10.3969/j.issn.1001-5078.2019.08.019 YUE D Q, MA J, LI J G, et al. Design of ROIC for LWIR hyperspectral detector[J]. Laser & Infrared, 2019, 49(8): 1014-1018(in Chinese). DOI: 10.3969/j.issn.1001-5078.2019.08.019

[8] ZHU Y J, NIU Y Z, LU W G, et al. A 160×120 ROIC with non-uniformity calibration for silicon diode uncooled IRFPA[C]// 2019 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC). New York, USA: IEEE Press, 2019: 1-3.

[9] 张武康, 陈洪雷, 丁瑞军. 具有背景抑制功能的长波红外读出电路[J]. 红外与激光工程, 2021, 50(2): 20200266. ZHANG W K, CHEN H L, DING R J. Long wavelength infrared readout circuit with background suppression function[J]. Infrared and Laser Engineering, 2021, 50(2): 20200266(in Chinese).

[10] 张淏洋, 陈洪雷, 丁瑞军. 一种改进型天文应用低噪声红外探测器读出电路结构设计[J]. 半导体光电, 2019, 40(3): 328-332. ZHANG H Y, CHEN H L, DING R J. An improved design of ROlC for ultralow noise infrared detector[J]. Semiconductor Optoelectro-nics, 2019, 40(3): 328-332(in Chinese).

[11] 刘晓磊, 喻松林. 长波红外焦平面读出电路设计分析[J]. 激光与红外, 2009, 39(2): 119-122. DOI: 10.3969/j.issn.1001-5078.2009.02.001 LIU X L, YU S L. Design analysis of ROIC for LWIR application[J]. Laser & Infrared, 2009, 39(2): 119-122(in Chinese). DOI: 10.3969/j.issn.1001-5078.2009.02.001

[12] WANG X, SHI Z L. Research on optimization of CTIA ROIC structure[J]. Microelectronics & Computer, 2014, 31(11): 64-68.

[13] 翟永成, 丁瑞军. 320×256大电荷容量的长波红外读出电路结构设计[J]. 红外与激光工程, 2016, 45(9): 80-85. ZHAI Y Ch, DING R J. 320×256 LW IRFPA ROIC with large charge capacity[J]. Infrared and Laser Engineering, 2016, 45(9): 80-85(in Chinese).

[14] 张露漩, 袁媛, 李敬国. 背景暗电流抑制的红外探测器读出电路输入级设计[J]. 激光与红外, 2021, 51(1): 69-73. ZHANG L X, YUAN Y, LI J G. Input stage design of IR detector readout circuitwith background dark current suppression[J]. Laser & Infrared, 2021, 51(1): 69-73(in Chinese).

[15] LI J H, WANG Y Sh, YU M Y, et al. A novel piecewise curvature-corrected CMOS bandgap reference[C]// 2008 7th International Caribbean Conference on Devices: Circuits and Systems IEEE. New York, USA: IEEE Press, 2008: 1-5.

[16] SPADYD, IVANOV V. A CMOS bandgap voltage reference with absolute value and temperature drift trims[C]// 2005 IEEE International Symposium on Circuits and Systems. New York, USA: IEEE Press, 2005: 3853-3856.

[17] LI J H, ZHANG X B, YU M Y. A 1.2 V piecewise curvature-corrected bandgap reference in 0.5 μm CMOS process[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2010, 19(6): 1118-1122.

[18] 崔佳旭, 李志远, 孙艳梅. 一种高PSRR带隙基准电压源的设计[J]. 黑龙江大学自然科学学报, 2022, 39(5): 597-603. CUI J X, LI Zh Y, SUN Y M. Design of a high PSRR bandgap vol-tage reference[J]. Journal of Natural Science of Heilongjiang University, 2022, 39(5): 597-603(in Chinese).

[19] 赵晨曦. 低功耗带隙基准电压源的研究与设计[D]. 成都: 电子科技大学, 2023: 20-44. ZHAO Ch X. Research and design of low power bandgapreference voltage source[D]. Chengdu: University of Electronic Science and Technology of China, 2023: 20-44(in Chinese).

[20] 梁清华, 蒋大钊, 陈洪雷, 等. 基于分时共享方案的640×512红外读出电路设计[J]. 红外与激光工程, 2017, 46(10): 246-253. LIANG Q H, JIANG D Zh, CHEN H L, et al. Design of 640×512 infrared ROIC based on time-sharing method[J]. Infrared and Laser Engineering, 2017, 46(10): 246-253(in Chinese).

[21] 蔡晶晶, 刘晓东, 张轩雄. 红外焦平面CTIA型读出电路的设计研究[J]. 上海理工大学学报, 2017, 39(4): 346-352. CAI J J, LIU X D, ZHANG X X. Design of CTIA readout circuit for IREPA[J]. Journal of University of Shanghai for Science and Technology, 2017, 39(4): 346-352(in Chinese).

[22] 王霄, 史泽林. CTIA型读出电路结构优化研究[J]. 微电子学与计算机, 2014, 31(11): 64-68. WANG X, SHI Z L. Research on optimization of CTIA ROIC structure[J]. Microelectronics & Computer, 2014, 31(11): 64-68(in Chinese).

下载:

下载: